# LX1686 Direct Drive CCFL Inverter Design Reference

George Henry Microsemi – Power Management Group

Copyright © 2000 Rev. 1.5, 9.01

## **Contents**

| 1.0 | INTRODUCTION RangeMAX vs. Analog Dimming                 |      |

|-----|----------------------------------------------------------|------|

|     |                                                          |      |

| 2.0 | WHAT IS DIRECT DRIVE?                                    |      |

|     | High Voltage Transformers for Direct Drive               |      |

|     | Designing for Cost                                       |      |

|     | Lamp Strike Voltage Generation                           |      |

|     | Standard Safety Features                                 |      |

|     | RangeMAX Digital Dimming                                 | 6    |

| 3.0 | A COMPARISON OF CONVENTIONAL "BUCK/ROYER" INVERTERS WITH |      |

| ••• | MICROSEMI'S "DIRECT DRIVE" TOPOLOGY                      | 7    |

|     |                                                          |      |

| 4.0 | THE LX1686 CCFL CONTROLLER IC                            | 8    |

|     | Block Diagram                                            | 8    |

|     | Dimming Control                                          | 8    |

|     | PWM Ramp Generator                                       | 8    |

|     | PWM Controllers                                          | 9    |

|     | BIAS Generator                                           | 9    |

|     | Output Drivers                                           |      |

|     | Timing Diagrams and Wavforms                             | . 10 |

| 4.2 | FUNCTIONAL PIN DESCRIPTION                               | . 11 |

| 4.3 | PACKAGE DIMENSIONS                                       | . 12 |

| 4.4 | BIAS & TIMING EQUATIONS REFERENCE                        | . 12 |

| E 0 | DESIGNING INVERTER MODULES WITH THE LX1686               | 42   |

| ე.ሀ |                                                          |      |

|     | Generating An On-Board VDD Supply For The LX1686         |      |

|     | Driving The ENABLE Input                                 |      |

|     | Logic Input Threshold Voltage                            |      |

|     | Setting Main Oscillator Frequency                        |      |

|     | Setting TRI C Ramp Frequency                             |      |

|     | Driving The BRITE Input                                  |      |

|     | BRITE Pin DC Input Operating Voltage Range               |      |

|     | Pointers Using PWM Inputs For Brightness Control         |      |

|     | Synchronizing The Digital Dimming Burst Rate             |      |

|     | AFD Circuit Response Time                                |      |

|     | Maximum VCO Frequency                                    |      |

|     | Compensating The Phase Detector                          |      |

|     | PLL Damping Factor                                       |      |

|     | High Frequency Attenuation Capacitor C7                  |      |

|     | Selecting U2, The Power FET                              |      |

|     | AOUT And BOUT Connections                                |      |

|     | The High Current Power Stage                             | . 16 |

|     | Configuring The High Voltage Output                      |      |

|     | High Voltage Feedback                                    |      |

|     |                                                          | 4-   |

|     | Short-Circuit Protection  Open Lamp Sensing              |      |

| Lamp Current Regulation Loop                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compensating The Error Amplifiers             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

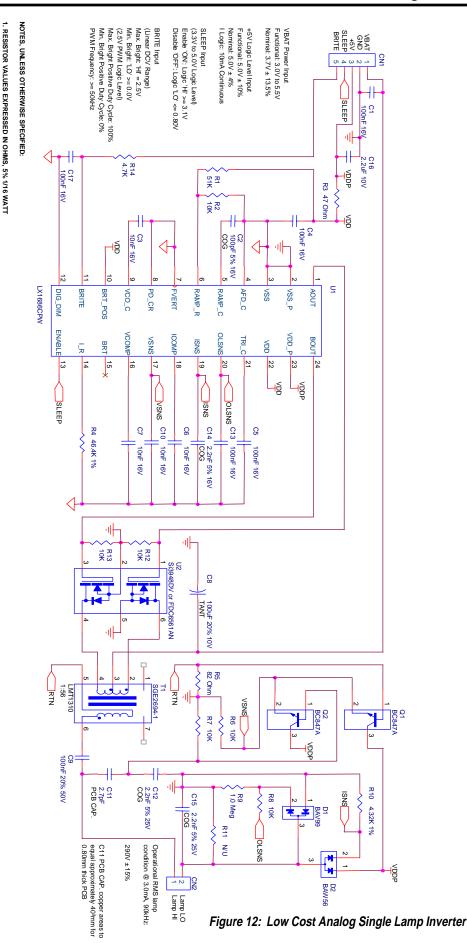

| Lowest Cost Configuration                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BRITE Input Signal Conditioning               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A Broken Lamp Shut Down Circuit               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRANSFORMER DESIGN and SELECTION CRITERIA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bifilar-Wound Primary                         | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Leakage Inductance                            | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Open Circuit Series Resonance                 | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Sufficient "Q" at Resonance                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transformer Turns Ratio                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Estimating Minimum Primary Voltage            | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Estimating Maximum Secondary Running Voltage* | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Turns Ratio                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Required Number of Secondary Turns            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Required Number of Primary Turns              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Determination of Primary Wire Gauge           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | Lamp Current Regulation Loop Compensating The Error Amplifiers Lowest Cost Configuration BRITE Input Signal Conditioning A Broken Lamp Shut Down Circuit  TRANSFORMER DESIGN and SELECTION CRITERIA  Bifilar-Wound Primary Leakage Inductance Open Circuit Series Resonance Sufficient "Q" at Resonance Transformer Turns Ratio Estimating Minimum Primary Voltage Estimating Maximum Secondary Running Voltage* Turns Ratio Required Number of Secondary Turns Required Number of Primary Turns Determination of Primary Wire Gauge Conclusion of Winding Analysis |

### 1.0 INTRODUCTION

Two equally important but technically diverse components determine overall performance, reliability and cost of CCFL inverters. One is the control integrated circuit; the other is the high voltage transformer. Since Microsemi is the only manufacturer that designs and manufactures both of these critical components, we alone are able to develop completely optimized modular solutions.

Microsemi Microelectronics has created the next generation in CCFL inverter topology with its patented new **LX1686** Direct Drive integrated circuit architecture. The **LX1686** backlight controller IC provides all the control functions necessary to implement Microsemi Direct Drive CCFL inverters . CCFLs are used for back or edge lighting of liquid crystal flat panel displays (LCD's) and typically find application in notebook computers, web browsers, automotive and industrial instrumentation, and entertainment systems. This IC can be used to control single or multiple lamp configurations.

This application note provides a guide for using this new control circuit in your module and magnetic designs. A comlete functional description of the chip is included, along with an applications information section in which typical module schematics are explained as an example to designers.

Direct Drive offers distinct advantages over conventional Buck/Royer inverters. These advantages are illustrated with practical examples and comparisons so that you may make informed decisions about which technology is best for your application.

The **LX1686** backlight controller IC includes a PWM (Pulse Width Modulation) controlled lamp current burst circuit that can provide greater than a 100:1 dimming range from a simple zero to 2.5V potentiometer input. The lamp current burst rate may be easily synchronized to the LCD panel's frame rate to prevent interference from optical beating between the two frequencies.

Safety and reliability features include dual feedback loops that permit regulation of maximum strike voltage as well as lamp current. Regulating maximum lamp voltage permits the designer to simultaneously provide for ample worst case lamp voltage while conservatively limiting maximum open circuit voltage.

An innovative new strike voltage generation technique enables the module designer to optimize high voltage transformer design for maximum efficiency while the lamp is ignited. The high voltage drop on the output ballast capacitor needed for Royer oscillators is much less, reducing transformer size and power dissipation.

### **LX1686 FEATURES**

- RangeMAX<sup>™</sup> Wide Range Dimming (>100:1)

- Dimming Burst Rate Synchronizable to Display Video Frequency

- High Voltage Feedback Loop Regulates Maximum Open Lamp and Minimum Strike Voltages

- Transformer Protected from Overheating During Lamp Striking

- Micro-Amp Sleep Mode

- User-Programmable Fixed Frequency Operation

- Under-Voltage Lockout Feature with Power-Up Reset

- Built-In Soft-Start Feature

- · Operates with 3.3V or 5V Power Supplies

- 50mA Output Drive Capability

### **APPLICATIONS**

- Notebooks

- Instrumentation Displays

- Desktop Computer Monitors

- Low Ambient Light Displays (Used in Aircraft, Automobiles and Hand-Held Equipment)

### **BENEFITS**

- Extremely High Efficiency from 3.3V, 5V and 12V Power Supplies

- Lower Cost than Conventional Buck/Royer Inverter Topologies

- Patented Strike Voltage Generation Method Ensures Lamp Ignition While Increasing Efficiency

- Fool-Proof Output Voltage Regulation Prevents Over-Voltage Failures

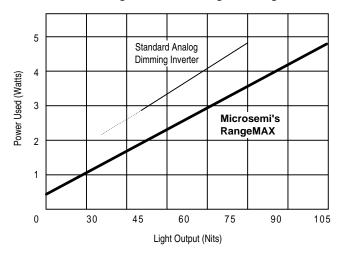

### RangeMAX vs. Analog Dimming

### 2.0 WHAT IS DIRECT DRIVE?

"Direct Drive" refers to the ability of Microsemi's new architecture to eliminate the inductor and resonant capacitors necessary to implement a conventional Royer oscillator based inverter solution. Instead, Direct Drive topology uses a fixed frequency PWM control circuit connected directly to a high voltage transformer primary via a pair of N-FET drivers. Removing these costly and power-hungry components simultaneously improves module cost, efficiency and size.

A two transistor N channel drive scheme was selected over popular bipolar and complementary P/N channel FET drives for three significant reasons:

- Using ground referenced transistors in conjunction with "push-pull" transformer operation permits the IC to be implemented with a low cost 5V fabrication process such as CMOS. This process permits the smallest die size, very high performance, and direct compatibility with 5V and 3.3V system power buses. The IC can interface through external N-FETs to any system voltage desired by simply changing the high voltage transformer turns ratio. Thus, an operating input voltage range for the module from 3V to more than 50V is possible.

- N-FETs are significantly more efficient switches than bipolar transistors or P-FETs of equal size and cost.

- Dual N-FETs are readily available in small surface mount packages at prices that compete favorably with the installed cost of bipolar transistors and their required additional circuit components.

Direct Drive topology is a non-resonant, fixed frequency PWM regulation method for operating CCFLs. The **LX1686** allows a wide choice of operating frequencies to match the lamp's most efficient operating point, and to minimize high frequency interference.

### **High Voltage Transformers for Direct Drive**

Direct Drive's push-pull transformer design provides important technical advantages when used in low voltage applications such as notebook computers and hand-held battery operated products.

Because of its dual primary winding construction, the voltage impressed across the primary in Direct Drive modules is twice the supply voltage. This is electrically equivalent to a four transistor "full or H-bridge" drive configuration and makes for very efficient operation at low voltages. Direct Drive topology enables efficient inverters that can run directly from 3.3 and 5V logic supplies now common in LCD panels.

Unlike Royer oscillator implementations, Microsemi's new approach for lamp strike voltage generation relieves the transformer from operating continuously at full lamp strike voltage once the lamp is ignited. Direct Drive transformers can be optimized for normal operation where they spend most of their life. Transformers can be smaller while system reliability is improved because the extra high voltage required to strike a CCFL is only present for the instant it is required. High voltage corona discharge, which gradually destroys insulation material, can be more easily avoided with Direct Drive designs (see the detailed description of strike voltage generation below).

Microsemi has developed completely new transformers to be used with our LX1686 control IC. The first two are 6 watt units that can drive lamps having strike voltages of up to 1800Vrms. The smaller of these permits modules to be built with maximum profiles of 10.5mm wide by 6mm high while operating at a very conservative 18V per mil voltage stress in air. Microsemi develops and works with other world class manufacturers to develop transformers for other applications as needed. A two lamp magnetic now in development will support up to 2500Vrms strike and 12W operating power. A magnetic design guide is included in this note to help you design your own magnetics if ours do not meet your exact needs.

### **Designing for Cost**

Continuous cost reduction is a way of life in the computer industry. Higher performance at ever decreasing cost is fundamental for success. Direct Drive topology takes this principle and applies it to LCD backlighting. For fixed input voltage dimmable inverter applications, the Microsemi solution provides the most efficient, least expensive, and smallest size available. Coupled with a step-down input voltage regulator, Direct Drive can handle extremely wide input voltage range applications while providing higher reliability and more features per dollar than older technologies.

### **Lamp Strike Voltage Generation**

Prior to the introduction of Direct Drive technology, the need to generate strike voltages more than twice the operating voltage of a lamp have limited transformer size reduction. The number of lines of flux required to generate strike voltage governs transformer minimum size. The number of lines of flux available in a magnetic structure is directly proportional to both core cross-section (Ae), and operating frequency.

Instead of increasing the physical size of the transformer, Microsemi chose to increase frequency, but only during lamp strike time when very high voltage output is needed. This allows the transformer to be sized for normal run voltages, resulting in a smaller design for a given power level. Smaller core structures have lower losses which helps improve inverter efficiency.

The LX1686 integrated circuit ramps operating frequency slowly up and down over a user adjustable range when the open lamp sense input (OLSNS) indicates the lamp is not ignited. The high voltage transformer and output capacitance have an unloaded self-resonant frequency that is higher than normal operating frequency. As strike frequency is increased, unloaded resonance is approached, resulting in a resonant rise of voltage across the output capacitance of the lamp, and the lamp is ignited. Since the unloaded resonance circuit has a high Q, typically in the range of 5 to 10, it is easy to generate very high strike voltages. At the same time, transformer flux density is maintained at low levels due to the higher frequency, preventing magnetic saturation.

This technique also solves the problem of the lamp's parasitic capacitance to ground forming a voltage divider with the ballast capacitor placed between the transformer secondary and the lamp.

In Royer oscillator designs, the lamp ballast capacitor is usually in the range of 12 to 22 pico Farad in order to drop excess transformer output voltage after the lamp has ignited. Direct Drive designs reduce transformer output voltage after ignition, permitting ballast capacitance values to be much larger.

The 100nF ballast (In this application it is really a DC bypass cap) typically used in Direct Drive transfers far more of the available transformer voltage to the lamp. For example, if a 22pF the available transformer voltage to the lamp. For example, if a 22pF ballast capacitor is used for a backlight assembly with 10pF of parasitic capacitance across the lamp, only 69% of the voltage generated by the transformer is available to strike the lamp. If this same back light assembly uses a 100nF ballast, 100% of available voltage is impressed across the lamp at strike time. Said another way, the Direct Drive transformer needs to develop only 6% more output than maximum lamp voltage, while the Royer design must develop 31% more! Clearly, strike capability is enhanced while transformer size and reliability are improved.

### **Standard Safety Features**

Microsemi's new Direct Drive controller includes an active open circuit voltage regulation feedback loop to prevent hazardous voltages, even if the lamp is removed from the circuit. When an open lamp condition is detected, the controller automatically enters strike mode as described above, and at the same time operates at 50% duty cycle to limit average power dissipation of the module to levels that can be maintained indefinitely. The module designer can select the open circuit voltage regulation point by choosing values of a non-dissipative capacitor voltage divider placed on the output terminals.

Lamp short circuit protection is inherent because lamp current is regulated even when lamp voltage is zero. Shorts from either lamp terminal to ground may also be protected by sensing all or part of the lamp current at the low voltage end of the transformer secondary winding.

### **RangeMAX Digital Dimming**

The LX1686 provides both current amplitude modulated dimming circuitry, which typically achieves between 3:1 and 5:1 dimming range and "Range MAX" time modulated lamp current circuitry that can easily achieve dimming ratios of 100:1. While duty cycle control of CCFL lamp current is not new, the LX1686 is the first CCFL control IC to completely integrate the function. The user interface for both dimming modes is the familiar DC control voltage or potentiometer.

Amplitude modulation brightness control differences a 0 to 2.5V (or optionally a 2.5 to 0V) analog brightness control voltage from a voltage developed by sampling current flow through the lamp. The resulting error signal is used to regulate lamp current amplitude between user definable minimum and maximum values.

In Digital Dimming mode, the same analog brightness control voltage is processed to modulate lamp current duty cycle. In this case, lamp current is either "on" at a user determined rms value, or off. The ontime duty cycle determines brightness of the lamp. Duty cycle can be controlled from nearly zero to 100% by the analog control voltage. Lamp brightness adjustment by duty cycle control is possible without the turn-on stress that occurs when the lamp is initially ignited, because the burst repetition rate is high enough to prevent lamp gasses from de-ionizing between current pulses.

The LX1686 "bursts" current on and off in a smooth and precisely controlled manner, eliminating turn-on overshoot that could shorten lamp life and pulse-to-pulse jitter that could cause flickering. An onchip PLL can synchronize lamp current bursts to an external sync pulse connected to the FVERT pin. This feature is important in high quality displays because it prevents optically visible beat frequencies between the lamp burst rate and the video frame rate. When an external sync pulse is used, the PLL multiplies the external frequency by 2 resulting in a burst frequency twice the sync input frequency. If the FVERT pin is left floating, lamp current burst frequency will free run at approximately 260Hz.

6

# 3.0 A COMPARISON OF CONVENTIONAL "BUCK/ROYER" INVERTERS WITH MICROSEMI'S "DIRECT DRIVE" TOPOLOGY

### **BUCK / ROYER ADVANTAGES:**

- Step-down voltage regulator (Buck regulator) adjusts input voltage to Royer oscillator, providing both line and load regulation.

- Lamp brightness is extremely insensitive to both static and dynamic input voltage changes. Conversion efficiency is fairly constant across input voltage range.

- Self-resonant Royer oscillator (transformer, ballast cap, PPS cap) provides low crest factor sine wave current waveform to the lamp. CCFLs operate most efficiently with low (1.4 to 1.6) crest factors.

### **BUCK / ROYER DISADVANTAGES:**

- 1. Requires more components, resulting in higher cost and larger size.

- Four power semiconductors, two power inductors and one PPS (Poly Phenelene Sulfide) high current capacitor burn power, reducing conversion efficiency. Very high quality components can be selected to regain some of these power losses, but high cost premiums and larger size must be paid.

- Open circuit voltage is very difficult to limit due to multiple resonances in the power circuit, lack of voltage feedback, and lack of frequency control from the controller IC. These circuits are prone to arcing and self destruction when operated open circuit (lamp unplugged or broken).

- Buck regulator and Royer oscillator operate asynchronously at different frequencies, making EMI and RFI more difficult to control.

# ROYER OSCILLATOR BALLAST CAP 22pF INDUCTOR SHTDWN BRT CONTROLLER

Figure 1: Buck/Royer Simplified Circuit

**BUCK REGULATOR**

### **DIRECT DRIVE ADVANTAGES:**

- Single stage PWM power conversion requires only two power transistors to provide line and load regulation. A very high efficiency dual N-Channel FET in an SO-8 package handles up to 10W.

- Non-resonant, fixed frequency drive eliminates inductor and high current resonant capacitor, reducing cost and size while increasing conversion efficiency.

- 3. Simplified high voltage transformer has one less winding and two less pins (smaller form factor = lower cost).

- Higher value ballast cap requires less transformer output voltage while lamp is ignited for additional efficiency and/or smaller size transformer is realized

- Active open circuit output voltage regulation is achieved via non-dissipative capacitor feedback from the transformer, eliminating open circuit hazards forever without costly (and sometimes ineffective) thermal protection devices being thermally bonded to the power transformer.

### **DIRECT DRIVE DISADVANTAGES:**

1. PWM regulation causes high lamp current crest factors when input voltage is more than 1.5 times the design minimum. This reduces nits/watt efficiency at high-line to approximately the same as a typical Buck/Royer design. At low-line (battery voltage levels) efficiency is 10-30% higher than Buck/Royer inverters. Direct Drive efficiency is so high at 5V and 3.3V that it makes up for Buck regulator losses in notebook systems, yielding comparable overall system efficiency while completely eliminating the disadvantage of high crest factors at high input voltages.

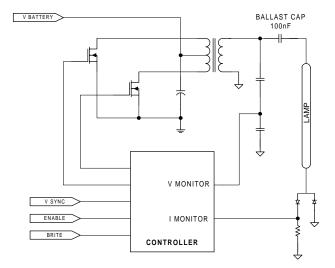

Figure 2: Direct Drive Simplified Circuit

### 4.0 THE LX1686 CCFL CONTROLLER IC **Block Diagram BRT ISNS VSNS** VCOMP ICOMP PD\_CR Output **PWM** Voltage Controllers Drivers Error Phase Voltage Output Detector Comparato Steering UDD P Logic VAMP 2.5V FVERT [ VCOMP ☐ AOUT Auto $\mathsf{L}_{\mathsf{ov}}$ IAMP VCO Freq. Detect **ICOMP** Current Current Comparator ☐ BOUT 0.5 - 2.5V RAMP\_DOUT USS\_P Burst Comparator RAMP C Bias Generator, CLK UVLO, and V<sub>REF</sub> BRITE 📋 ENA ≶50k PWR GD 2.50V VDD\_SW 50k Open Lamp FNABLE VDD VDD 300mV Triangle Ignite Wave Generator BRT\_POS **PWM** Ramp DIG\_DIM 🗀 Generator **Dimming Control** RAMP\_C RAMP R TRI C OLSNS

### Figure 3: LX1686 Simplified Block Diagram

### **Dimming Control**

- Performs the frequency locking for a 2V<sub>pp</sub> ramp oscillator with oscillation frequency that locks to the LCD display vertical scanning frequency. Frequency locking is done by a 3rd order phase-lock loop formed by the phase detector, VCO and the divide-by-2 TF/F. The phase detector is a 3-state charge pump type that allows easy filtering and loop compensation. The VCO is a voltage-controlled ramp oscillator with fixed output voltage levels (0.5 to 2.5V). When there is no external FVERT detected by the Auto-Freq-Detector, the VCO will oscillate at 5.5/10.5 its maximum frequency. The VCO can be forced to oscillate at 5.5/10.5 of its maximum oscillation frequency by grounding Pin AFD C.

- Performs BRITE voltage inversion (determined by BRT\_POS pin voltage) and passes the converted voltage to BRT for analog and digital dimming. The BRITE signal is buffered by a MUX before connection to the internal op amp so that during SLEEP Mode or Power-Down, BRITE is isolated from internal circuitry to ensure no chip biasing occurs through the BRITE pin.

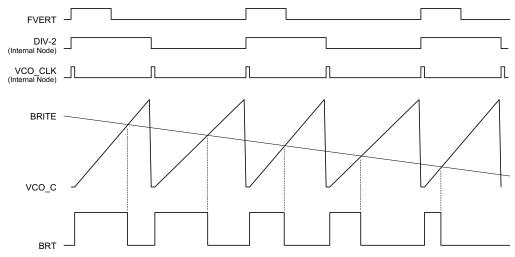

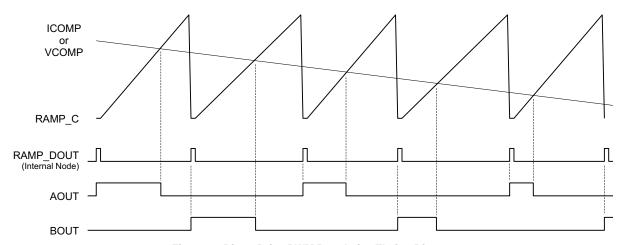

- Performs the generation of a digital dimming PWM signal derived from the VCO's ramp output with the burst comparator and the external analog DC input (BRITE) as shown in the timing diagram Figure 4. When digital dimming is selected, this signal is used to generate a 2.5V pulse muxed to port BRT. When analog dimming is selected, then either BRITE's DC voltage or its inversion will be muxed to the BRT port.

Pin BRT\_POS is used to control BRITE polarity during digital and analog dimming. When BRT\_POS is "1", the regulated lamp current will be proportional to BRITE's voltage. When "0", the current will be inversely proportional to BRITE's voltage.

### **PWM Ramp Generator**

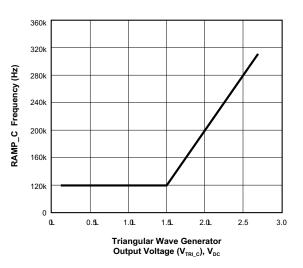

- Performs the generation of a 2 V<sub>PP</sub> ramp oscillator whose oscillation frequency can be changed through the voltage imposed on the input port TRI\_C as shown in Figure 5. When TRI\_C voltage is below 1.5V, the ramp oscillates at the normal run frequency. When TRI\_C is above 1.5V, the ramp oscillation frequency will be proportional to V<sub>TRI\_C</sub>. When TRI\_C is at 2.25V, the ramp will oscillate at a higher frequency, depending on the R RAMP value. This ramp oscillator provides 2 timing signals for the controller: analog ramp output RAMP\_C and digital ramp output RAMP\_DOUT. Both of these outputs are used by the controller PWM block, in conjunction with the dimming output BRT, to create two digital PWM outputs (AOUT and BOUT) that operate in push-pull fashion.

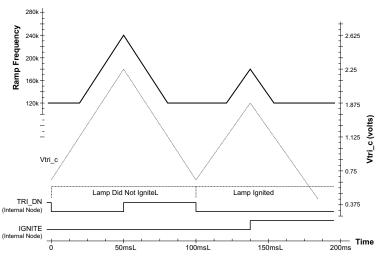

- Performs frequency sweeping during CCFL startup mode (pre-strike) and run mode (post-strike). The tasks are performed and controlled by an approximately 10Hz triangular wave generator. The triangular analog output (V<sub>TRI\_C</sub>) swings from 0.75 to 2.25V. Normally, V<sub>TRI\_C</sub> will be reset at 0V, waiting to be ramped up. When the lamp is off,

detected by pin OLSNS, the triangular wave generator will start to ramp up. It takes about 25ms to ramp up to 1.5V; this time is used for the PWM block to settle out such that it can perform lamp current regulation. After reaching 1.5V,  $V_{\mathsf{TRL}_{.C}}$  will continue to ramp up and increase the RAMP\_C frequency. Increase in ramp frequency will increase lamp voltage due to the CCFL backlight transformer parasitic LC resonance. Increase in lamp voltage will in turn improve lamp ignition probability. After the lamp ignites, detected again by OLSNS,  $V_{\mathsf{TRL}_{.C}}$  will start ramping down and decrease the RAMP frequency slowly back to nominal. Lamp ignition is indicated by an internal signal called IGNITE. The lamp striking timing and sequence are illustrated in Figure 6. If the lamp fails to ignite when  $V_{\mathsf{TRL}_{.C}}$  reaches 2.25V,  $V_{\mathsf{TRL}_{.C}}$  will ramp down. During this ramp down time AOUT and BOUT signals are turned OFF to prevent transformer overheating.

Both the ramp generator and the triangular wave generator are reset during low power supply voltage.

### **PWM Controllers**

- Performs voltage and current regulation functions. Timing is shown in Figure 7.

- Performs transformer output voltage regulation by comparator VCOMP and error amplifier VAMP. The error amplifier generates an error voltage derived from the voltage difference between VSNS and the internal 1.25V reference. The error voltage is compared with RAMP\_C by VCOMP to generate two PWM signals (A, B) that drive two output buffers. These two buffers drive two external power FET switches that can increase or decrease the transformer output voltage. By feeding back the transformer voltage through pin VSNS, a negative feedback loop is formed to regulate the maximum transformer output voltage to a predetermined value.

- Performs lamp current regulation by comparator ICOMP and the

error amplifier IAMP. The error amplifier generates an error voltage

derived from the voltage difference between ISNS and BRT. The

error voltage is compared by ICOMP with RAMP\_C to generate

two PWM signals (A, B) that drive the same two output buffers. By

feeding back the lamp current through a sense resistor network to

pin ISNS, a negative feedback loop is formed to regulate the lamp

current to a set value determined by BRT voltage.

- All PWM flip-flops are reset and the VCOMP pin is discharged during power-up.

### **BIAS Generator**

- Performs the power-down functions controlled by the ENABLE input.

The power-down mode is activated by forcing ENABLE low. During

the power-down mode, internal power supply voltage VDD\_SW is

turned off and no DC power is available to any internal circuitry

except the ENABLE circuitry. The main source of Sleep Mode

operating current is from the ENABLE pin internal pull-up resistor

(100k to VDD).

- Performs the Under-Voltage-Lock-Out (UVLO) function. Internal ports PWR\_BD and PWR\_GD are used to indicate whether VDD voltage is acceptable for reliable internal circuit operation. PWR\_BD and PWR\_GD are valid when VDD voltage is above 1.3V. VDD\_P voltage is not monitored.

- Performs voltage and current bias generation. An internal 2.5V voltage regulator for precision voltage biasing is generated by a bandgap circuit. An internal precision current bias is generated through an external resistor R<sub>1</sub> at pin I\_R. This precision current bias is copied four times and distributed to four circuit blocks.

### **Output Drivers**

- Performs buffering function for the signals A and B from the PWM block.

- Port PWR\_BD is used to ensure pins AOUT and BOUT will stay low during power startup or when VDD voltage is below the UVLO threshold (about 2.8 V).

- Pins VDD\_P and GND\_P are used to isolate high-current power and ground from the low signal power and ground terminals (VDD, GND). This is done to reduce switching noise coupling.

### **Timing Diagrams and Wavforms**

Figure 4: Digital Dimming Timing Diagram

Figure 5: RAMP\_C Frequency vs. V<sub>TRI C</sub>

Figure 6: Lamp Ignition Timing Diagram

Figure 7: Direct Drive PWM Regulation TIming Diagram

10

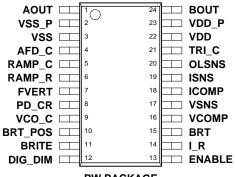

### 4.2 FUNCTIONAL PIN DESCRIPTION

| Pin<br>Number          | Pin<br>Designator | Description                                                                                                                                                                                                              |  |  |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                      | AOUT              | Output driver A.                                                                                                                                                                                                         |  |  |

| 2                      | VSS_P             | Power ground for output drivers only.                                                                                                                                                                                    |  |  |

| 3                      | VSS               | Signal ground.                                                                                                                                                                                                           |  |  |

| 4                      | AFD_C             | Connects to an external cap, $C_{AFD}$ . Forcing to ground or VDD will make the VCO oscillate at approximately 50% of the maximum VCO frequency. Forcing to VDD/2 will make the VCO oscillate at 2x the FVERT frequency. |  |  |

| 5 RAMP_C Connects to e |                   | Connects to external capacitor $C_{\text{RAMP}}$ for setting Direct Drive PWM operating frequency.                                                                                                                       |  |  |

| 6                      | RAMP_R            | Connects to external resistor R <sub>RAMP</sub> for setting Direct Drive PWM operating frequency.                                                                                                                        |  |  |

| 7                      | FVERT             | Vertical frequency reference digital input. Has internal pull down.                                                                                                                                                      |  |  |

| 8                      | PD_CR             | Phase Detector Filter. Part of phase lock loop. Connects to external capacitor and resistor network.                                                                                                                     |  |  |

| 9                      | VCO_C             | Connects to external capacitor C <sub>VCO</sub> .                                                                                                                                                                        |  |  |

| 10                     | BRT_POS           | Brightness polarity control. Has internal pullup. Leave open or pull up to VDD for dimming brightness proportional to BRITE voltage, connect to ground for brightness inversely proportional to BRITE voltage.           |  |  |

| 11                     | BRITE             | Analog voltage input for brightness control.                                                                                                                                                                             |  |  |

| 12                     | DIG_DIM           | Digital Dimming Enable internal pullup. Leave open or pull up to VDD for operating in digital dimming mode. Connect to ground for analog dimming mode.                                                                   |  |  |

| 13                     | ENABLE            | Chip Enable internal pullup. High enables the chip. Low disables.                                                                                                                                                        |  |  |

| 14                     | I_R               | Current Reference Resistor. External resistor to ground (Ri) determines internal reference currents.                                                                                                                     |  |  |

| 15                     | BRT               | Current Error Amplifier non-inverting input.                                                                                                                                                                             |  |  |

| 16                     | VCOMP             | Voltage Error Amplifier output. Connects to external frequency compensation capacitor $C_{\text{VCOMP}}$ . Controls soft-start timing. $C_{\text{VCOMP}}$ not needed for amplifier stability.                            |  |  |

| 17                     | VSNS              | Voltage Error Amplifier inverting input.                                                                                                                                                                                 |  |  |

| 18                     | ICOMP             | Current Error Amplifier output. Connects to external frequency compensation capacitor C <sub>ICOMP</sub> . C <sub>ICOMP</sub> not needed for amplifier stability.                                                        |  |  |

| 19                     | ISNS              | Current Error Amplifier inverting input.                                                                                                                                                                                 |  |  |

| 20                     | OLSNS             | Open Lamp Sense Input. Lamp assumed ingnited if V <sub>OLSNS</sub> ≥ 300mV.                                                                                                                                              |  |  |

| 21                     | TRI_C             | Connects to external capacitor $C_{TRI}$ for setting strike frequency ramp slope.                                                                                                                                        |  |  |

| 22                     | VDD               | VDD                                                                                                                                                                                                                      |  |  |

| 23                     | VDD_P             | Dedicated VDD for output buffers only.                                                                                                                                                                                   |  |  |

| 24                     | BOUT              | Output driver B.                                                                                                                                                                                                         |  |  |

PW PACKAGE (Top View)

Figure 8: Pin Diagram

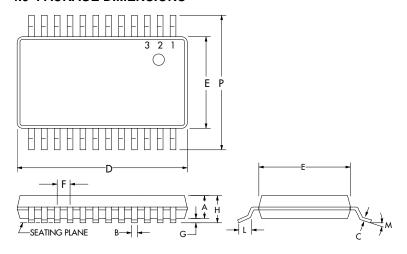

### 4.3 PACKAGE DIMENSIONS

|     | Millim  | neters | Inches    |        |  |

|-----|---------|--------|-----------|--------|--|

| Dim | Min.    | Max.   | Min.      | Max.   |  |

| Α   | 0.85    | 0.95   | 0.033     | 0.037  |  |

| В   | 0.19    | 0.3    | 0.007     | 0.012  |  |

| С   | 0.09    | 0.2    | 0.0035    | 0.008  |  |

| D   | 7.7     | 7.9    | 0.303     | 0.311  |  |

| Е   | 4.3     | 4.5    | 0.169     | 0.177  |  |

| F   | 0.65    | BSC    | 0.025 BSC |        |  |

| G   | 0.05    | 0.15   | 0.002     | 0.005  |  |

| Н   |         | 1.1    |           | 0.0433 |  |

| L   | 0.5     | 0.75   | 0.02      | 0.03   |  |

| М   | 0       | 8      | 0         | 8      |  |

| Р   | 6.4 BSC |        | 0.252 BSC |        |  |

| *LC |         | 0.1    |           | 0.004  |  |

<sup>\*</sup> Lead Coplanarity

Note:

Figure 9: PW (TSSOP) 24-pin Package Dimensions

### 4.4 BIAS & TIMING EQUATIONS REFERENCE

Equation 1:

$$I_PD = I_VCO = I_RAMP = I_TRI = \frac{1.0V}{Ri}$$

[A]

Where I\_PD, I\_VCO, I\_RAMP and I\_TRI are internal nodes. Capacitor charge currents flowing out of PD\_CR, VCO\_G, RAMP\_C and TRI\_C are various multiples of the current flowing in Ri. These multiples are taken into account in the following equations.

**Equation 2:** Triangular Wave Generator Frequency

$$F_{TRI} = \frac{1}{(30 \cdot Ri \cdot C_{TRI})} [Hz]$$

Equation 3: Ramp Generator Frequency, F<sub>RAMP</sub> in Hz

If

$$V_{TRI,C} \leq 1.5V$$

then

$$F_{RAMP} = 0.72 \cdot \frac{(1 + VDD/20)}{(Ri \cdot C_{RAMP} + 0.5 \text{ sec})} = F_{O}$$

If

$$V_{TRLC} > 1.5V$$

then

$$F_{BAMP} = (1 + 0.75 \cdot (V_{TBL,C} - 1.5) \cdot (N - 1)) \cdot F_{O}$$

$$F_{RAMP\ MAX} = N \cdot F_O$$

where

$$F_{_{

m O}}$$

=  $F_{_{

m RAMP}}$  during run-mode (at  $V_{_{

m TRI\_C}}$  < 1.5V) N = Maximum  $F_{_{

m RAMP}}$  multiplier

**Equation 4:** N = Maximum Frequency Multiplier

$$R_{RAMP1} = \frac{VDD \cdot Ri}{4(N-2)}$$

$$R_{RAMP2} = \frac{VDD \cdot Ri}{\frac{8}{4}(N-1) \cdot VDD - 4 \cdot (N-2)}$$

**Equation 5:** Maximum VCO Frequency

$$F_{VCOMAX} = \frac{1}{(5 \cdot Ri \cdot C_{VCO})} [Hz]$$

Equation 6: Maximum Phase Detector Output Current

$$I_{PD} = \frac{1}{10 \cdot Ri} [A]$$

Equation 7: PLL PD High-Frequency Attenuation Capacitor

$$C_{PDC} = 0.1 \cdot C_{PD}$$

Equation 8: PLL Zero Time Constant

$$T_7 = R_{PD} \cdot C_{PD}$$

[sec]

Equation 9: PLL VCO Gain

$$K_{VCO} = 2 \cdot \frac{\pi}{(Ri \cdot C_{VCO})}$$

**Equation 10: PLL Natural Frequency**

$$W_N = (1/2) \cdot \sqrt{\frac{K_{VCO}}{(2 \cdot \pi \cdot N \cdot Ri \cdot C_{PD})}}$$

[radian]

$$W_{N} = \frac{1}{\left(2 \cdot Ri \cdot \sqrt{N \cdot C_{VCO} \cdot C_{PD}}\right)} [Hz]$$

Equation 11: PLL Damping Factor

$$D_{F} = \left(\frac{T_{Z}}{2}\right) \cdot W_{N}$$

$$D_F = 0.5 \cdot R_{PD} \cdot C_{PD} \cdot W_N$$

[see Equation 8]

Dimensions do not include mold flash or protrusions; these shall not exceed 0.15mm (.006") on any side. Lead dimension shall not include solder coverage.

Equation 12: PLL Approximated Pull-In Time

$$T_{P} = \frac{(16 \cdot \pi)}{W_{N}} \text{ [sec]}$$

Equation 13: Auto-Frequency Detection Response Time

$$T_{DAFD} = 2,000,000 \cdot C_{AFD}$$

[sec]

Equation 14: Soft-Start Time

$$T_{ss} = 450,000 \cdot C_{VCOMP}$$

[sec]

Equation 15: Minimum Error Amp Bandwidth

$$BW_{EA\_MIN} = \frac{0.000048}{C_{ICOMP}} [Hz]$$

# 5.0 DESIGNING INVERTER MODULES WITH THE LX1686

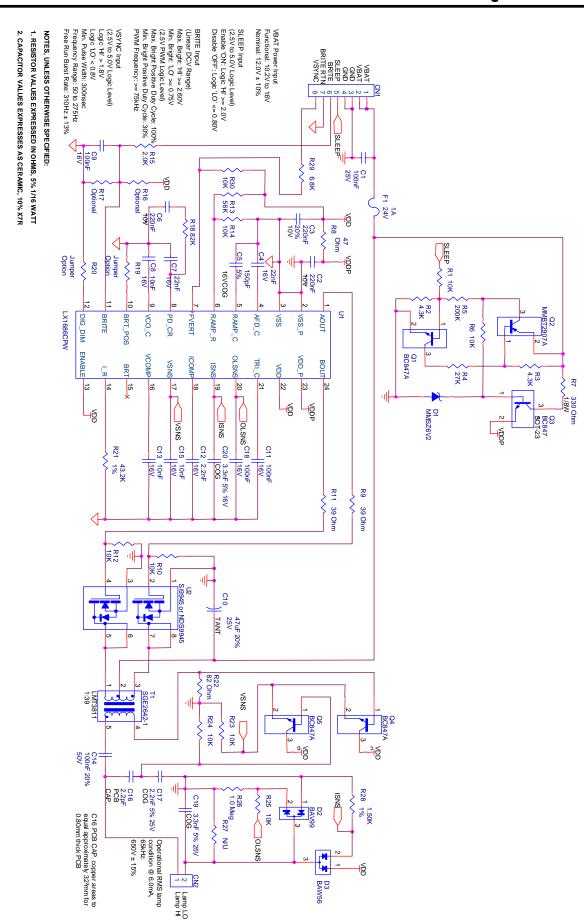

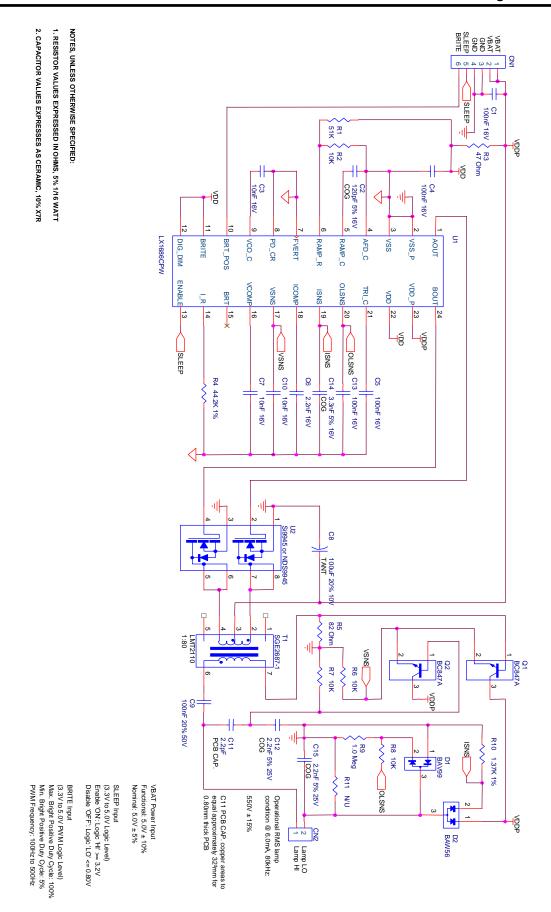

This section gives the design procedure for a typical inverter module similar to the Microsemi standard LXM1612-12-01. It is designed to operate from a single 10.8 to 13.2 volt power supply, and will drive a single lamp with a run voltage in the range of 550 to 750V<sub>RMS</sub>. The inverter includes an on-board regulator to provide VDD for the LX1686, a zero power sleep mode circuit, and signal filtering on the BRITE input that will accept either DC voltages or a PWM logic input to control lamp current. Lamp current may be optionally controlled in either analog (amplitude modulated) or digital (duty cycle modulated) fashion. The schematic for this circuit is shown in Figure 10.

This design specifies an available Microsemi designed high voltage transformer. Please see Appendix A for information about designing custom transformers. Equations for calculating circuit component values are summarized in Section 4.5. Additional module variations follow this basic design.

### **Getting Started**

First, select the bias current resistor for the LX1686. The value of R21 determines magnitude of four internal current sources that set timing parameters. These are phase detector slew rate; digital dimming burst oscillator frequency, triangle generator frequency, and main oscillator frequency. R21 is normally set around 40K ohms, but may be in the range of 20k to 60K. This design uses 43.2K 1%. While its value is not critical, R21 temperature coefficient should be very low to prevent parameter drift. Bias current is 1.00 volt divided by R21. Various ratios of this current will be sourced from pins 5, 8, 9, and 21. Note that this resistor affects all four functions stated, so it must be selected first.

Next decide if you will be using the analog or digital dimming method, and the polarity of the dimming signal. If you use digital dimming, connect pin 12 (DIG\_DIM) to VDD. It may alternately be left open because it has an internal 100K pull-up to VDD. If you choose analog dimming mode, connect pin 12 to ground. This design has an optional jumper (R20) in the design to permit easily changing methods.

The LX1686 includes an amplifier that can be used to invert the sense of the BRITE pin. If pin 10 (BRITE\_POS) is pulled up to VDD, lamp current will increase for increasing voltage on BRITE. If grounded, lamp current will increase for decreasing voltage on BRITE. This pin has an internal 100K pull-up as well, but may be terminated directly to VDD. This design also includes an optional jumper (R19) to permit easily reversing BRITE sense.

Now is a good time to consider filtering the IC power input pins. There are two VDD inputs, pin 22 (VDD) feeds all analog signals, and pin 23 (VDD\_P) feeds only the output drive stage. These need to be filtered separately. We recommend 220nF ceramic capacitors on each pin (C2 And C3) although 100nF is sufficient if the trace layouts are very short and wide. VDD needs a 47 ohm resistor (R8) to help filter power stage switching transients from the analog control circuits. This is particularly important when using digital dimming, as any noise on the supply can act as an unwanted input at the BRITE pin and cause lamp current jitter. This will appear as lamp flicker.

C1 is added to reduce conducted emissions onto the power line. It should be a ceramic type with good high frequency characteristics, and must be located directly across the input connector power pins to be effective.

### Generating An On-Board VDD Supply For The LX1686

The LX1686 can operate with VDD and VDD\_P from 3.0 to 6.0V. If a supply in this range is not available, it can be generated on the inverter module. For best efficiency VDD should be high enough to fully enhance the FET (U2) at turn on. This design uses a 4.5 volt  $\rm V_{GS}$  FET and sets VDD nominal at 5.3 volts to insure full enhancement under worst case component tolerances. If you are using less than a five volt supply, select a 2.7 volt  $\rm V_{GS}$  FET for U2.

The VDD linear regulator must supply 7mA maximum operating current for the LX1686 plus another 5 to 10mA average for switching the FETs. Design for 17 mA to insure that worst case conditions are met.

A transistor switch circuit that is driven with the ENABLE input precedes the regulator. It removes VDD from the LX1686, eliminating its quiescent current drain when ENABLE is low. Remaining battery load is limited to leakage current of the three transistors and the filter capacitors.

Q1 and Q2 form a non-inverting high side switch that draws no current when the base of Q1 is less than 0.5 volts. R1 and R2, together with Q1  $V_{\rm BE}$  set input threshold to 2.0 volts. When Q1 turns on, Q2 saturates. R5 provides positive feedback to Q1 generating hysterisis to prevent partial turn on if input rise time is very slow. R6 and D1 establish a 6.2 volt reference that is buffered by emitter follower Q3. R7 is placed in series with Q3 collector to reduce its power dissipation. C2 is an X7R ceramic filter capacitor for VDD\_P. R8 and C3, another X7R, filter switching noise from the LX1686 VDD input. Both C2 and C3 must be located so their connections to U1 use very short and wide traces.

$$V_{DD} = V_{D1} - Q1_{VBE} - R8 \cdot I_{VDD}$$

$V_{DD} \cong 6.2 - 0.6 - 0.3$   $V_{DD} \cong 5.3V$

### **Driving The ENABLE Input**

In the example described directly above, ENABLE is connected to VDD so the LX1686 will be turned on when its power is applied. ENABLE may also be driven by a CMOS or TTL logic signal to cause the LX1686 to enter sleep mode. A low on this line is sleep and a high is active. If this later method is used, the switch circuit comprised of Q1 and Q2 is not needed. Instead, connect the open end of R6 to Vbat. Sleep current in this configuration will be approximately 1mA.

### **Logic Input Threshold Voltage**

It is possible to have different voltages on VDD for the LX1686 and on the logic chip that drives ENABLE or other logic inputs such as FVERT and BRT\_POS (as used in Figure 10). A common example is 5.3V on the LX1686 and 3.3V on its driver IC. Since logic threshold voltage for the LX1686 is VDD/2 + 0.6V, it will be necessary to provide a positive bias to the LX1686 inputs. Adding a 6.8K series resistor at the input terminal and a 10K pull-up to VDD at the LX1686 pin easily does this. R29 and R30 illustrate this circuit on the FVERT pin. Voltage on the FVERT pin will be 2.62V when the SYNC input is 0.8 volts and 3.93V when SYNC is at 3.0V. These values center the 3.3V FVERT threshold between worst case input levels from the driver.

### **Setting Main Oscillator Frequency**

The main oscillator controls lamp current frequency. It is a linear ramp generator that runs at twice the frequency of the output stage. Two frequency limits must be programmed for this oscillator,  $F_{\text{RAMP}}$  and  $F_{\text{RAMP MAX}}$ . When the inverter is operating normally with the lamp ignited, OLSNS will be greater than 300mV indicating lamp ignition.

This locks the oscillator at  $F_{\text{RAMP}}$ .  $F_{\text{RAMP}}$  is programmed by the values of R21 and C5. When the inverter is in 'strike mode' (lamp is not ignited) OLSNS will be less than 260mV, and oscillator frequency is placed under control of the voltage ramp on the TRI C pin. As TRI C voltage increases above 1.5 volts, frequency is slowly ramped to  $F_{RAMP\ MAX}$ . The values of R13 and R14 determine F<sub>RAMP MAX</sub>. The equations below are written for a value N that is the ratio of maximum over minimum frequency. Most inverter designs should be set up for N = 3 to insure adequate strike voltage can be produced, e.g., open circuit resonance of the high voltage transformer and parasitic load capacitance can be reached during strike mode. N may be increased to as high as 5 for designs using very high turn's ratio transformers. These are generally needed for striking 1400Vrms or higher lamps from a very low input voltage such as a single cell Lithium-ion battery. It is a good idea to measure the resonant frequency of your transformer wired to its actual load before choosing 'N'. Units in the following equations are volts, ohms, farads, and Hertz.

$$F_{RAMP} = \frac{0.72 \left(1 + \frac{VDD}{20}\right)}{R21 \cdot C5 + 0.5 \cdot 10^{-6}}$$

$$C5 = \frac{0.72 \left(1 + \frac{VDD}{20}\right)}{R21 (F_{PAMD})} - \frac{0.5 \cdot 10^{-6}}{R21}$$

$$F_{RAMP\_MAX} = N \cdot F_{O}, \qquad N = Maximum F_{RAMP} \text{ multiplier}$$

$$R13 = \frac{VDD \cdot R21}{4 (N-2)}$$

$$R14 = \frac{VDD \cdot R21}{\frac{8}{3} VDD (N-1) - 4 (N-2)}$$

Using these equations to calculate values:

VDD = 5.3V (determined previously)

R21 = 43.2K (determined previously)

$F_{RAMD} = 130KHz, N = 3$  (assumed)

C5 = 152.36pF (Use 150pF, 5%, COG to allow for PCB trace capacitance and low T.C.)

R13 = 57.2K (Use 57.6K, 1% or 56K, 5%)

R14 = 9.44K (Use 9.53K, 1% or 10K, 5%)

### Setting TRI\_C Ramp Frequency

The signal at pin 21, TRI\_C, controls the main oscillator frequency during the lamp striking process. TRI\_C is low, near zero volts, when the lamp is operating. When in strike mode, TRI\_C is a triangular waveform that varies between .75 and 2.25 volts. The frequency of the triangle wave is proportional to the value of C11, the capacitor on pin 21. Frequency should be in the range of 2 to 20Hz. For convenience, we use a 100nF X7R capacitor that gives an operating frequency of:

$$F_{TRI} = \frac{1}{30 \cdot R21 \cdot C11}$$

$$F_{TRI} = \frac{1}{30 \cdot 43.2K \cdot 0.1F} = 7.7Hz$$

$$C11 = \frac{1}{30 \cdot R21 \cdot F_{TRI}}$$

### **Driving The BRITE Input**

The BRITE input connects to an inverting op amp (Av = -1) and a comparator. Depending on the state of BRT\_POS, the comparator will be connected to either the input or the output of the op amp. In either case, the op amp output is connected to the BRITE pin through its feedback resistors. The resistors are each 50K ohms (See Figure 3 Block Diagram). Since the op amp will force its inverting input to be 1.5 volts independent of BRITE's voltage, the equivalent BRITE input circuit becomes 50K ohms terminated to a 1.5V power supply. Input current to the BRITE pin ranges from 0 to +/-  $30\mu$ A, and flows into the pin for signals lower than 1.5V. In order to minimize this loading effect on dimming linearity and range, source impedance of the BRITE signal should be much lower than 50K. While op amp gain accuracy is excellent due to 1% matching of these two feedback resistors, their absolute values can vary up to +/- 30% including lot to lot process

variations and temperature coefficient of resistance. This needs to be considered in applications requiring extreme accuracy and repeatability of brightness control, and usually requires the BRITE input be driven with a low impedance op amp. In this design we use a simple 2K ohm RC low pass filter that gives performance suitable for a notebook computer display. This filter can convert a high frequency PWM signal to a DC voltage compatible with the BRITE pin, or pass a DC voltage directly from a potentiometer or DAC.

### **BRITE Pin DC Input Operating Voltage Range**

The DC input operating voltage range for the BRITE pin is 0 to 3 volts if in analog dimming mode (DIG\_DIM is low) and 0.5 to 2.5 volts if in digital dimming mode (DIG\_DIM is high). The abbreviated digital dimming range insures the burst comparator can produce both 0% and 100% duty cycles by making the voltage ramp on its inverting input have top and bottom limits that can be over ridden by the BRITE input voltage of 0 to 3 volts. The top and bottom points of the ramp are set at 2.5 and 0.5V respectively by an internal 2% reference voltage to provide good accuracy and repeatability for the  $V_{\rm BRITE}$  vs. lamp current transfer function. Dimming ratios of 100:1 are possible.

### **Pointers Using PWM Inputs For Brightness Control**

Many microprocessors have PWM output channels available for controlling external analog functions. These channels may be programmed to output variable width pulses at various repetition rates. Since the LX1686 needs a DC control voltage at its bright input, it is necessary to change the PWM signal to DC with a low pass filter. In Figure 10, the BRITE filter has a time constant of 2K x 100nF = 200µs. This will not adequately filter a PWM input signal (If PWM frequency is less than 75 KHz). If using a PWMinput, increase the value of C9 to make its time constant with R15 atleast 20 times the period of the PWM pulses. For example,  $100\mu$ Fgenerates a 200ms time constant that will adequately filter 100Hzand above. If filtering is inadequate, ripple voltage on the BRITE pin will cause lamp current modulation at the PWM repetition rate, and ifripple frequency is lower than 90Hz, will appear as visible flicker.

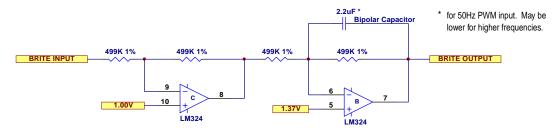

Remember also, that DC voltage output from the filter is proportional to input duty cycle *and input voltage amplitude*. If BRITE signal amplitude is not constant, additional circuitry is needed to prevent its variations from changing the lamp current. A universal conditioning circuit is shown in Figure 13 that clamps any pulse amplitude above 2.5 volts while still passing a DC input without changing it. The circuit has 500K input impedance so it is more tolerant of high source impedance. Its large time constant integrator can filter PWM inputs as slow as 50Hz, but it uses low frequency op amps which limit maximum input frequency to 1 or 2KHz. High speed op amps can be substituted if higher PWM frequencies are desired.

The optional resistor divider, R16 and R17 (Figure 10) can be used to set a lower limit on BRITE voltage, even if the source voltage goes to ground. This can guarantee a minimum brightness level, and, in the case digital dimming is used, provide a hardware 'stop' that will keep the BRITE input far enough above the VCO valley voltage to prevent entering strike mode. This is discussed in more detail when we deal with the OLSNS input circuit.

### **Synchronizing The Digital Dimming Burst Rate**

The LX1686 has a complete PLL on chip to permit an external signal to control burst rate. An AFD circuit (Auto Frequency Detect) automatically looks for a logic signal input on the FVERT pin. If one is detected, the PLL locks to it and generates an internal burst rate at exactly twice its frequency. Doubling burst frequency insures an ability to synchronize to low 50 and 60Hz frame rates while still having a burst rate above visual detection. Actually, the PLL can lock to any frequency between 40 and 200Hz. The polarity and duty cycle of FVERT may be anything as long as a minimum pulse width of 300ns is presented. Pulse polarity can even change on the fly without loosing phase lock. This is important in portable applications because the video sync signal can have different width and polarity in various programs. A classic case is during boot up on a notebook where DOS and Windows generate different V<sub>SYNC</sub> polarity.

### **AFD Circuit Response Time**

AFD circuit response time is controlled by C4. An internal current source alternately charges and discharges C4 with a square wave that is generated by dividing the signal at FVERT by two. If FVERT is present, the voltage at AFD\_C will stabilize at VDD/2. If FVERT is static high or low, the voltage at AFD\_C will stabilize at either VDD of VSS accordingly. Comparators sample this voltage to determine if a signal is present. Response time is a function of the current source amplitude set by R21 and the value of C4 as follows:

$$T_{D-AFD} = 50 \cdot R21 \cdot C4$$

$$C4 = \frac{T_{D-AFD}}{50 \cdot R21}$$

A 22nF X7R capacitor will result in about 0.48 second response, a good place to start.

### **Maximum VCO Frequency**

Digital dimming burst frequency is the same as VCO frequency. Maximum VCO frequency (Fvco\_max) must be designed for two times the maximum expected frequency on the FVERT pin, e.g., Fvco\_max = 2 FVERTmax. If no signal is detected on FVERT, the VCO defaults to ½ its maximum design value.

This feature can be used to set nominal burst frequency when no synchronization input is used.

$$F_{VCO\_MAXI} = 2 FVERT_{MAX} = \frac{1}{5 \cdot R21 \cdot C8}$$

For FVERT expected maximum equals 100Hz,  $F_{VCO\ MAX} = 200Hz$ .

Then:

$$C8 = \frac{1}{5 \cdot R21 \cdot F_{VCO\_MAX}}$$

$$C8 = \frac{1}{5 \cdot 43.2K \cdot 200} = 23nF$$

The closest smaller standard value is 22nF, which gives actual maximum VCO frequency of 210Hz. If no input is placed on the FVERT pin, typical burst frequency is 210/2 = 105Hz. This is about as low as you should go to prevent visual detection of lamp current bursts. If you want to calculate C8 to provide a specific 'unsynchronized' burst frequency;

$$C8 = \frac{1}{5 \cdot R21 \cdot 2 \cdot F_{VCO\ TYPICAL}}$$

Assuming  $F_{VCO\ TYPICAL}$  is 230Hz;

$$C8 = \frac{1}{5.43.2 \text{K} \cdot 2.200} = 10 \text{nF}$$

### **Compensating The Phase Detector**

C6, C7, and R18 values determine phase detector pull-in time (time to lock to a new frequency) and damping factor. The phase detector amplifier is a Gm type and has a maximum output current,  $I_{\rm PD}=1/10\cdot R21$ . This current is in the range of 2µA, so low leakage ceramic capacitors must be used for C6 and C7 to prevent erratic operation. Pull-in time in the range of 0.1 to 1 second is usually acceptable. If too long, however, the lamp may flash on power up as the VCO changes from the initial default frequency to the lock frequency (remember, the VCO will default to  $F_{\rm VCO~MAX}/2$  until PLL lock is achieved). The damping factor is usually set to 0.707 (critically damped).

### Pull-in time:

$$T_P = \frac{16 \cdot \pi}{W_N}$$

, where  $W_N$  is the natural PLL frequency.

$$W_{N} = \frac{1}{2 \cdot R21 \cdot \sqrt{10 \cdot C8 \cdot C6}}$$

$$T_P = 32 \cdot \pi \cdot R21 \cdot \sqrt{10 \cdot C8 \cdot C6}$$

$$C6 = \frac{T_{p}^{2}}{(32 \cdot \pi \cdot R21)^{2} \cdot (10 \cdot C8)}$$

For Pull-in time of 0.7 seconds: C6 = 220nF

For Pull-in time of 0.5 seconds, C6 = 100nF

### **PLL Damping Factor**

$$D_F = \left(\frac{T_Z}{2}\right) \cdot W_N$$

, where  $T_Z$  is the PLL zero time constant,

$T_Z = R18 \cdot C6$

$$R18 = 4 \cdot D_F \cdot R21 \cdot \frac{\sqrt{10 \cdot C6 \cdot C8}}{C6}$$

For Damping factor = 0.707, C6 = 220nF, C8 = 10nF, and R21 = 43.2K,

$$R18 = 82K$$

### **High Frequency Attenuation Capacitor C7**

This capacitor reduces high frequency gain of the loop.

$$C7 = \frac{C6}{10}$$

For  $C6 = 220$ nF,  $C7 = 22$ nF

If you are not using synchronized digital dimming do not install C4, C6, C7, and R18. Instead, connect pins 4 and 8 to analog ground.

### Selecting U2, The Power FET

Drain to source voltage rating for U2 should be 3 to 4 times the maximum power supply voltage. In this push – pull topology, operating  $V_{\rm DS}$  is twice  $V_{\rm BAT}$  due to the dual primary winding on the high voltage transformer. Because these windings are impossible to perfectly match, especially with respect to leakage inductance, there will be an inductive spike at transistor turn off. Its amplitude is proportional the leakage inductance difference of the two winding halves.  $V_{\rm GS}$  needs to be high enough to survive these spikes. Some design trade-offs are possible.  $V_{\rm GS}$  can be increased to permit more imbalance in the transformer construction, or snubbers can be added on the transistor drains to suppress the transients. Snubbers generally dissipate power, and in doing so reduce efficiency. Another possibility is to select a FET having an adequate repetitive avalanche power rating to absorb transient energy without overheating. This will also reduce efficiency.

On state resistance of the FET should be less than 200 milli ohms for a typical 4 to 6 Watt load. It can be increased for lighter loads. Experience shows that reducing Rds\_on below 100 milli ohms increases efficiency very little. For highest efficiency, it is better to select a FET with very low total gate charge. At 60 to 80KHz, gate losses can be larger than the I<sup>2</sup>R losses of a 100 milli-ohm FET pair.

$V_{\rm GS}$  is an important selection parameter. The LX1686 drive voltage to the FET gates is equal to the VDDP supply. Select FET's that are fully enhanced at the minimum supply voltage. This design uses an on board generated VDDP that operates at 5.6V nominal to give the FET's a bit more drive.

### **AOUT And BOUT Connections**

The 10K resistors (R10 and R12) to ground on these pins pull down the FET gates when input supply voltage is too low to guarantee the state of the LX1686 outputs. This typically occurs below 2.5V. If the supply is increased very slowly through the 1 to 2.5 volt levels, it is possible to inadvertently turn the FET's on at 100% duty. This could blow the input fuse or destroy the FET's. If slow power on cannot happen in your system, the 10K resistors may be omitted.

Thirty nine ohm resistors R9 and R11 are connected in series with the gates and work with FET input capacitance to slow down their transition time. This reduces high frequency emissions and helps control EMI. Care must be taken to *not* make R9 and 11 too high, as slowing transition time too much will cause the FET's to overheat. Power losses are highest during transitions since current and voltage are both high then. If you choose a different FET, re-optimize R9 and R11 values.

### The High Current Power Stage

U2, T1 and C10 are the high current power stage components. Square wave switching currents pass through each of them. They must be designed for low resistance to minimize I²R losses, and must be physically positioned close together with extremely short conductors to prevent ground noise from interfering with the BRITE input, and to minimize radiated and conducted emissions. Further PC layout should have separate power and signal ground paths. Analog signal ground should connect to power ground only at the negative end of C10.

C10 is a low ESR tantalum in this design. Always use D or E case parts because they have the lowest ESR. Ceramic capacitors in the 2 to  $10\mu$ F range also work well but are more expensive.

### **Configuring The High Voltage Output**

High voltage is delivered to the lamp through C14, a series DC Bypass capacitor. Use a  $50V_{\text{DC}}$  or higher rated XR7 type capacitor. Maximum voltage appears across the capacitor when the output is shorted, because lamp current increases under short circuit conditions. The high voltage end of the lamp must be connected to this capacitor to maintain high efficiency. Actually the lamp itself is non-polarized, but when mounted in a panel, it takes on an important characteristic. One terminal will have a very short wire resulting in very low parasitic capacitance. The other's will be long, creating much higher parasitic capacitance. The concern is leakage currents flowing into this parasitic load, since they serve no good function, reduce efficiency, and complicate lamp current regulation. Since there is little voltage to flow parasitic current, the long wire is returned to the low voltage rectifier circuit.

The purpose of the ballast capacitor is to prevent any DC current in the lamp, as this drastically reduces its life, and to act as real impedance against the negative impedance of the lamp. Its value is chosen as high as possible to minimize voltage drop across it. Voltage across C14 is at a 90 degree phase shift with lamp voltage, so must be added vector wise to find total voltage required from the transformer. Note that with direct drive topology, it is not necessary to drop large voltages on the ballast capacitor, as is the case with Royer circuits.

One precaution: direct drive, as with all other known topologies, can experience a low frequency amplitude modulation of lamp current under certain conditions. This is caused by the negative resistance and extreme voltage dependency on temperature of the lamp operating in a current regulated closed loop. Check for modulation, usually in the 5 to 15KHz range while varying lamp current and power supply input voltage. Modulation can usually be eliminated by optimizing operating frequency.

### **High Voltage Feedback**

Lamp voltage is divided across capacitors C16 and C17 and fed back to the LX1686 VSNS input through emitter follower Q5. R24 DC restores C17 to keep the waveform at Q5 base sinusoidal. Q5 acts as

a rectifier and buffer, presenting a known fraction of peak lamp voltage to VSNS.

VSNS is the inverting input of the voltage error amplifier. Its characteristics are identical to, and its output is processed the same as the current error amplifier. Its non-inverting input is connected to a precision 1.25 volt DC reference. If the peak lamp voltage exceeds a preset limit by choosing the ratio of C16 and C17, AOUT and BOUT pulse widths will be reduced as needed to regulate peak lamp voltage.

Choose C16 in the range of 2 to 5pF, keeping it small to minimize leakage current and to keep unloaded resonant frequency below 300KHz so strike voltage is easily developed. Next choose C17 as a multiple of C16 so maximum peak voltage is equal to 1.25 volts plus Q5  $\rm V_{\rm BE}$ . If more freedom from Q5 temperature variation is desired, add a 3.3K resistor in series with R23 and ground to form a voltage divider. Connect the resistor tap to VSNS. Now  $\rm V_{\rm PK}$  max will be 3.75V plus Q5  $\rm V_{\rm BE}$ .

Microsemi has designed many inverters that use a PCB capacitor for C16. If space allows, this will save the relatively high cost of a low pico farad high voltage capacitor. Standard formulas for parallel plate capacitors apply, and we have found computer grade PCB materials to be a very acceptable dielectric. If you do this be sure to round all sharp corners and leave at least 3mm spacing between low and high voltage conductors to prevent arcing.

### **Short-Circuit Protection**

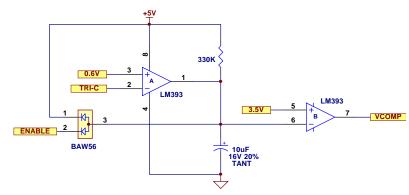

Underwriters Laboratory requires maximum peak current, for even a single cycle, be limited to a specific value when any of the output terminals and ground are shorted with a 2K ohm resistor. This can be a problem when shorting either lamp terminal to ground because the current sensing mechanism in the control loop is shorted. Under this situation, the loop will put out maximum possible current, which will always exceed UL's requirements. Q4 and R22 are added to this design to meet UL requirements for a "limited current device". R22 is selected so the voltage across it will regulate maximum short circuit current through Q4 and into the VSNS circuit, just like high voltage is regulated.